AMD ZEN2架构解析 7nm加持新增多条指令

作为首款使用7nm工艺的桌面级CPU,AMD的第二代ZEN2架构自然备受期待,根据台积电和国外媒体的研究报告显示,目前的7nm FF工艺对比10nmFF工艺有巨大的提升,具体为最高40%的功耗提升,但性能提升尚不详。

AMD Zen架构取得了空前成功,今年还优化为Zen+增强版,并有同样优化的12nm工艺辅助,而现在我们终于迎来了全新的第二代Zen 2架构,以及全新的7nm工艺加持。

AMD原计划采用GlobalFoundries 7nm为自家新CPU、GPU代工,但后者已经放弃7nm及后续工艺,好在还有天字一号代工厂台积电,AMD 7nm CPU、GPU全都转移了过去,而且目前看起来很顺利,无论产品设计还是路线图都在按计划进行。

根据台积电提供的数据,7nm相比于目前的14/12nm可以将晶体管密度提高一倍,同等频率下功耗可以降低一半,而同等功耗下性能提升可以超过25%。

如果说12nm更多地是在“数字”上领先Intel 14nm,这一次7nm则是在技术上完全实现超越,也能稍微领先Intel仍在难产的10nm。

更先进的制造工艺一直是Intel最强有力的武器,但这次竟然被AMD完全超越,实在是令人唏嘘,即便是Intel一再强调自己的10nm相当于其他家的7nm也无济于事,毕竟人家的产品马上就要出来了。

回到Zen 2,这是世界上第一个7nm工艺的高性能x86 CPU,除了新工艺主要变化包括:CPU核心执行增强、更深入的安全增强、模块化设计灵活配置并降低制造难度。

Zen 2实现了两倍于第一代的吞吐能力,这主要得益于执行流水下的改进、浮点单元和载入存储单元的翻番、核心密度的翻番、每操作功耗的减半。

在前端设计上,Zen 2重点改进和优化了分支预测、指令预取、指令缓存、操作缓存。

而在浮点方面,Zen 2将浮点宽度翻了一番达到256-bit,载入存储带宽同样翻了一番,并提升了分发/回退带宽,所有模块都保持着很高的吞吐。

安全性方面,AMD重点强调了新架构可以在硬件层面免疫Spectre幽灵安全漏洞。

Zen 2架构支持更多核心,但并不是单纯地增加核心数量,而是采用了特殊的组合结构:EPYC霄龙最多单路64核心128线程,分为八个Die,每个Die内八个物理核心,同时外部还有一个单独的I/O Die,集成内存控制器、Infinity Fabric高速总线、I/O输入输出,专门负责联络各个Die与物理核心。

这种新的模块化设计更加灵活,可以单独针对每个模块进行优化、调配,同时借助I/O Die大大优化了整体延迟与功耗。

不过注意,CPU Die部分用的是7nm工艺, I/O Die部分则还是14nm,因为后者大部分都是模拟电路,对新工艺并不敏感,即便上了7nm也不会带来集成度、性能、功耗的明显改善,成本却会明显增加,所以采用了这种混合工艺模块组合。

事实上,Intel也正在同一颗芯片内尝试不同工艺的组合,都是出于同样的目的。

以上说的都是Zen 2架构的理论部分,最终落实到EPYC霄龙、Ryzen锐龙产品上,还会有不同的表现,但可以预料,新架构新工艺,必然会带来明显更高的频率、更低的功耗,而且无论桌面还是服务器,AMD这几年都会保持前后代兼容。

AMD还首次确认,Zen 4架构已经在设计中,将在7nm+ Zen 3之后面世,时间上估计至少会在2021年。

相关文章

从去年开始,最让电脑用户振奋的大事件莫过于 AMD 的崛起了。去年 AMD Ryzen 处理器横空出世,打了“牙膏厂”英特尔一个措手不及,市场份额由之前的15%左右上升到31%。今2018-05-07

从去年开始,最让电脑用户振奋的大事件莫过于 AMD 的崛起了。去年 AMD Ryzen 处理器横空出世,打了“牙膏厂”英特尔一个措手不及,市场份额由之前的15%左右上升到31%。今2018-05-07

AMD二代锐龙单核性能不如intel 为什么还有用户会选择锐龙

目前intel八代酷睿处理器已经全面上市了,了解AMD二代锐龙和intel八代处理器的朋友们都清楚AMD二代锐龙单核性能远不如intel,那么,为什么还有用户会选择锐龙呢?对此,本2018-05-04

Ubuntu 18.04 LTS版已发布:AMD安全内存加密等多方面升级(附下载地址)

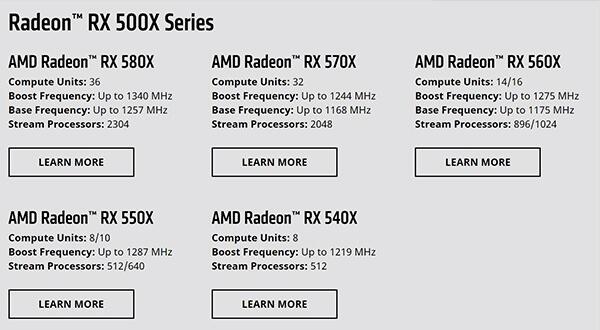

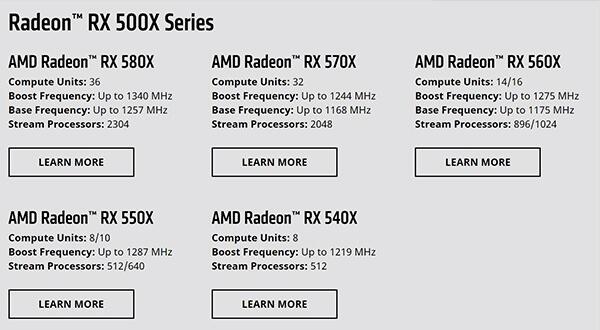

Ubuntu 18.04 LTS正式发布,在云计算领域效率极高,特别适用于机器学习这样的存储密集型和计算密集型任务,并且进行了多方面的升级,例如针对SATA Link电源管理等2018-04-28 AMD在今天凌晨正式发布了Radeon 500X系列显卡,主要面向于OEM市场,同时AMD也公布了这些显卡的参数,和之前所报道的一样,绝大部分的Radeon 500X系列显卡均为马甲卡2018-04-12

AMD在今天凌晨正式发布了Radeon 500X系列显卡,主要面向于OEM市场,同时AMD也公布了这些显卡的参数,和之前所报道的一样,绝大部分的Radeon 500X系列显卡均为马甲卡2018-04-12 据称AMD计划在4月19日推出新的2000系Ryzen二代处理器,性能反超一代的Ryzen 7 1800X,现在AMD已经在全球开启了新一轮的促销,海量的初代Ryzen处理器都处于最低价格2018-03-20

据称AMD计划在4月19日推出新的2000系Ryzen二代处理器,性能反超一代的Ryzen 7 1800X,现在AMD已经在全球开启了新一轮的促销,海量的初代Ryzen处理器都处于最低价格2018-03-20

最新评论